MODULE 5: CỖ MÁY THỜI GIAN (SEQUENTIAL LOGIC & FSM)

Chào bạn! Chúng ta đã đi qua hai “chân trụ” của logic tuần tự: Flip-flop (Trí nhớ) và Xung Clock (Nhịp tim). Giờ đây, chúng ta sẽ lắp ghép chúng lại để tạo ra “Bộ não” điều khiển mọi hoạt động của hệ thống. Bài học về Máy trạng thái (Finite State Machine – FSM) chính là chìa khóa để bạn chuyển từ việc thiết kế các mạch điện đơn lẻ sang thiết kế một hệ thống tự động hóa thông minh.

1. Giới thiệu

Chào mừng bạn đến với bài học về “Bộ chỉ huy” của mọi hệ thống số. Nếu bạn từng thắc mắc làm thế nào một chiếc máy giặt biết khi nào phải bơm nước, khi nào phải giặt và khi nào phải vắt, thì câu trả lời chính là Máy trạng thái (Finite State Machine – FSM).

Trong thiết kế FPGA với chip Artix-7 XC7A100T, FSM là công cụ mạnh mẽ nhất để quản lý các quy trình phức tạp. Khác với các dòng lệnh if-else chồng chéo trong phần mềm thường gây ra hiện tượng “treo” hoặc trễ, FSM trong FPGA được xây dựng từ các cổng logic và Flip-flop vật lý, giúp hệ thống chuyển đổi giữa các tác vụ một cách cực kỳ chính xác và tức thời.

Trong công nghiệp, từ bộ điều khiển tay máy robot đến các giao thức truyền tin tốc độ cao trên bo AIOT-ARTIX7, tất cả đều vận hành dựa trên “kịch bản” của FSM. Hiểu về FSM là bạn đã nắm giữ chìa khóa để thiết kế các hệ thống tự động hóa thực thụ.

2. Nội dung chính

2.1. Máy trạng thái là gì? – “Kịch bản của những tình huống”

Hãy tưởng tượng FSM là một bản kế hoạch gồm các “vòng tròn” (trạng thái) và các “mũi tên” (điều kiện chuyển đổi). Tại một thời điểm, hệ thống chỉ có thể ở duy nhất một trạng thái xác định.

- Trạng thái (State): Một công việc cụ thể đang được thực hiện (Ví dụ: Đang chờ, Đang mở cửa).

- Điều kiện chuyển (Transition): Một sự kiện xảy ra khiến hệ thống đổi sang việc khác (Ví dụ: Có người đi qua, Hết thời gian).

Ví dụ đời sống: Chiếc cửa tự động tại siêu thị

- Trạng thái 1 (Chờ): Cửa đóng im lìm.

- Sự kiện: Cảm biến phát hiện có người (Tín hiệu logic ‘1’).

- Trạng thái 2 (Mở): Động cơ quay để mở cửa.

- Trạng thái 3 (Giữ): Đợi 5 giây để người đi qua.

- Trạng thái 4 (Đóng): Động cơ quay ngược để đóng cửa khi hết thời gian và không còn người.

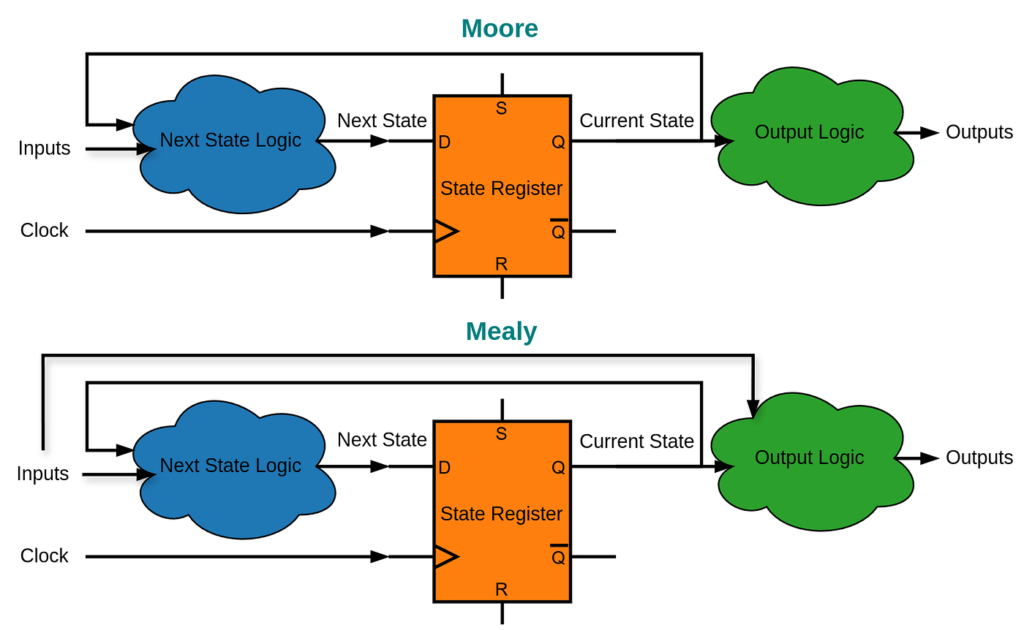

2.2. Cấu trúc của FSM bên trong chip Artix-7

Khi bạn thiết kế FSM trên bo mạch AIOT-ARTIX7, phần mềm Vivado sẽ tạo ra 3 khối phần cứng hoạt động song song:

- Bộ nhớ trạng thái (State Register): Sử dụng các Flip-flop để ghi nhớ câu hỏi “Tôi đang ở trạng thái nào?”.

- Logic chuyển trạng thái (Next State Logic): Các cổng logic tính toán xem “Dựa vào đầu vào hiện tại, bước tiếp theo tôi sẽ đi đâu?”.

- Logic đầu ra (Output Logic): Các cổng logic quyết định “Ở trạng thái này thì phải bật đèn nào, chạy mô-tơ nào?”.

2.3. Tư duy song song: FSM không bao giờ “ngủ”

Đây là điểm khác biệt cực lớn so với vi điều khiển (như nhân MPU trên i.MX93):

- Trong phần mềm: Khi bạn dùng lệnh

delay(5000) để đợi 5 giây, CPU thường bị “khóa” lại và rất khó xử lý việc khác cùng lúc.

- Trong FPGA: FSM sử dụng một bộ đếm chạy độc lập ở bên cạnh. Trong khi FSM đang ở trạng thái “Chờ 5 giây”, các phần mạch khác trong FPGA vẫn đang xử lý tín hiệu RF hoặc ADC một cách hoàn toàn song song. FSM chỉ đơn giản là đợi một tín hiệu “Xong rồi” từ bộ đếm để nhảy sang trạng thái kế tiếp.

2.4. Thực hành tư duy trên bo mạch AIOT-ARTIX7

Hãy tưởng tượng việc thiết kế một Bộ điều khiển Đèn giao thông đơn giản:

- Các trạng thái: XANH -> VÀNG -> ĐỎ.

- Điều kiện: Sử dụng một bộ đếm thời gian (nhờ xung Clock 50MHz).

- Đầu ra: 3 đèn LED trên bo mạch.

- Tương tác: Bạn có thể dùng một Nút nhấn (Button) làm tín hiệu “Ưu tiên người đi bộ”. Khi nhấn nút, FSM sẽ ngay lập tức tính toán để chuyển từ XANH sang VÀNG nhanh hơn bình thường. Bạn sẽ thấy mạch điện phản ứng cực kỳ nhạy bén vì nó được “đi dây” để ưu tiên xử lý sự kiện đó.

3. Tổng kết

- FSM là bộ não điều khiển: Giúp hệ thống thực hiện các công việc theo trình tự logic thông minh và chặt chẽ.

- Tính hữu hạn: Hệ thống luôn ở một trạng thái xác định, giúp tránh các lỗi logic không lường trước (“treo” máy).

- Sự kết hợp: FSM kết hợp cả Logic tổ hợp (tính toán điều kiện) và Logic tuần tự (ghi nhớ trạng thái bằng Flip-flop).

- Tốc độ FPGA: Việc chuyển trạng thái diễn ra ngay tại cạnh lên của xung Clock, đảm bảo tính thời gian thực (Real-time) tuyệt đối cho hệ thống.

Kiểm tra kiến thức

Hãy hoàn thành các câu hỏi trắc nghiệm dưới đây để kiểm tra tư duy về “Bộ chỉ huy” FSM.

- Câu 1: Trong Máy trạng thái (FSM), tại một thời điểm hệ thống có thể ở bao nhiêu trạng thái?

A. Nhiều trạng thái cùng lúc để xử lý song song.

B. Chỉ duy nhất một trạng thái.

C. Hai trạng thái: một trạng thái cũ và một trạng thái mới.

D. Không ở trạng thái nào cả.

Xem đáp án & Giải thích

Đáp án đúng: B

Giải thích: Theo định nghĩa của “Finite State”, tại mỗi thời điểm xác định, hệ thống chỉ có thể ở duy nhất một trạng thái hiện hành (Current State) để đảm bảo tính ổn định và logic.

- Câu 2: Thành phần nào bên trong FPGA chịu trách nhiệm “ghi nhớ” trạng thái hiện tại của FSM?

A. Các dây dẫn đồng.

B. Cổng logic AND/OR.

C. Các Flip-flop (Thanh ghi trạng thái).

D. Cổng USB-UART.

Xem đáp án & Giải thích

Đáp án đúng: C

Giải thích: Flip-flop là đơn vị cơ bản để lưu trữ thông tin trạng thái trong logic tuần tự. Tập hợp các Flip-flop tạo thành thanh ghi trạng thái (State Register).

- Câu 3: Điều gì kích hoạt việc chuyển từ trạng thái này sang trạng thái khác trong một FSM đồng bộ?

A. Khi người dùng tắt nguồn bo mạch.

B. Cạnh lên của xung Clock kết hợp với điều kiện đầu vào thỏa mãn.

C. Khi chip Artix-7 phát ra tiếng kêu.

D. Khi đèn LED bị cháy.

Xem đáp án & Giải thích

Đáp án đúng: B

Giải thích: Xung Clock đóng vai trò là nhịp điều phối. Tại cạnh lên của Clock, FSM sẽ kiểm tra các điều kiện đầu vào và logic chuyển trạng thái để quyết định xem có nhảy sang trạng thái mới hay không.

- Câu 4: Ưu điểm của việc dùng FSM trong FPGA so với dùng lệnh switch-case trong phần mềm là gì?

A. FSM trong FPGA được hiện thực bằng mạch cứng, chạy song song và không gây trễ hệ thống khi xử lý nhiều điều kiện đồng thời.

B. FSM dễ viết hơn ngôn ngữ C.

C. FSM không cần dùng đến xung Clock.

D. FSM có thể dự báo được thời tiết.

Xem đáp án & Giải thích

Đáp án đúng: A

Giải thích: Đây là ưu điểm về hiệu năng vật lý. FSM trong FPGA là một cấu trúc mạch điện song song, giúp phản ứng tức thì mà không bị ảnh hưởng bởi độ trễ thực thi lệnh tuần tự của CPU.

- Câu 5: Trong ví dụ cửa tự động, nếu đang ở trạng thái “Đóng cửa” mà cảm biến phát hiện có người, FSM thiết kế tốt sẽ làm gì?

A. Tiếp tục đóng cửa cho xong rồi mới tính tiếp.

B. Ngay lập tức chuyển sang trạng thái “Mở cửa” để đảm bảo an toàn.

C. Tắt nguồn hệ thống.

D. Chờ người dùng nhấn nút Reset.

Xem đáp án & Giải thích

Đáp án đúng: B

Giải thích: Đây là tính linh hoạt và phản ứng nhanh của FSM. Việc thiết kế kịch bản cho phép hệ thống ưu tiên các sự kiện quan trọng (như an toàn) để chuyển trạng thái ngay lập tức.

“Chúc mừng bạn đã hoàn thành Module 5! Bạn đã nắm giữ được tư duy thiết kế hệ thống điều khiển thông minh. Hãy sẵn sàng để ‘vươn vòi’ ra thế giới bên ngoài ở Module 6 nhé!”