MODULE 2: TƯ DUY “XÂY NHÀ” – TỪ CỔNG LOGIC ĐẾN MẠCH CHỨC NĂNG

Chào bạn! Rất vui được tiếp tục đồng hành cùng bạn trong hành trình khám phá thế giới vi mạch. Chúng ta đã học cách “phân loại” (Decoder) và “điều phối” (MUX) luồng dữ liệu. Bây giờ, chúng ta sẽ bước vào một bài học mang tính bước ngoặt: Dạy cho con chip Artix-7 cách làm toán.

1. Giới thiệu

Chào mừng bạn đến với bài học cuối cùng của Module 2. Nếu các bài trước giúp máy tính “nhận diện” và “lựa chọn”, thì bài học về Bộ cộng (Adder) sẽ biến nó thành một công cụ tính toán thực thụ. Mọi phép toán phức tạp như nhân, chia, hay thậm chí là xử lý đồ họa và trí tuệ nhân tạo (AI) đều được xây dựng dựa trên những phép cộng nhị phân đơn giản nhất.

Trong công nghiệp, bộ cộng là thành phần cốt lõi của các bộ điều khiển PID (điều khiển nhiệt độ, tốc độ động cơ) hay các hệ thống xử lý tín hiệu số (DSP). Với chip Artix-7 XC7A100T trên bo mạch AIOT-ARTIX7, việc làm toán không diễn ra bằng cách chạy từng dòng lệnh code như trên máy tính bạn đang dùng. Thay vào đó, nó sử dụng các đường dẫn vật lý song song để cộng hàng triệu con số cùng một lúc. Hiểu về bộ cộng, bạn sẽ thấy được vẻ đẹp của việc “toán học hóa” dòng điện và tại sao FPGA lại là “ông vua” của tốc độ tính toán.

2. Nội dung chính

2.1. Phép cộng nhị phân: Khi 1 + 1 không bằng 2

Trong hệ thập phân, 1 + 1 = 2. Nhưng trong hệ nhị phân (chỉ có hai chữ số 0 và 1), chúng ta không có chữ số “2”.

Quy tắc cộng nhị phân cơ bản:

- 0 + 0 = 0

- 0 + 1 = 1

- 1 + 0 = 1

- 1 + 1 = 0 (và nhớ 1 sang cột tiếp theo).

Khái niệm mới: Trong phần cứng, kết quả của phép cộng 1 bit luôn gồm 2 phần riêng biệt: Tổng (Sum) và Số nhớ (Carry).

2.2. Ví dụ đời sống: Cách chúng ta cộng tiền

Hãy tưởng tượng bạn đang cộng số tiền 15.000 + 7.000. Bạn cộng hàng đơn vị trước (0+0), sau đó đến hàng chục, hàng trăm. Khi đến hàng nghìn (5+7=12), bạn viết 2 và “nhớ” 1 sang hàng chục nghìn. Bộ cộng trong FPGA hoạt động y hệt như vậy, nhưng thay vì dùng 10 ngón tay, nó sử dụng các cổng logic để xử lý số “nhớ” này với tốc độ cực nhanh.

2.3. Bộ cộng bán phần (Half Adder) và Bộ cộng toàn phần (Full Adder)

Đây là những “mô-đun” xây dựng nên máy tính:

- Half Adder (Bộ cộng bán phần): Chỉ cộng được 2 số A và B. Nó dùng cổng XOR để tính Tổng và cổng AND để tính Số nhớ.

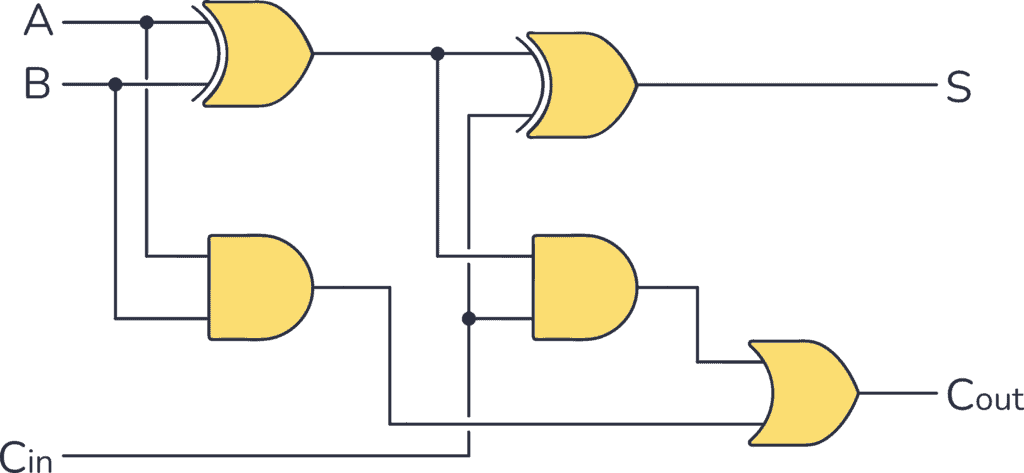

- Full Adder (Bộ cộng toàn phần): Đây mới là “siêu sao”. Nó có thể cộng A, B và cả số nhớ từ cột trước mang sang (Carry-in). Đây là cách chúng ta chồng các bộ cộng lên nhau để cộng những con số cực lớn (8-bit, 16-bit, 64-bit).

Full Adder logic circuit

2.4. So sánh: Phép cộng Phần mềm vs. Phần cứng

- Phần mềm (Vi điều khiển): Để cộng hai số, CPU phải lấy số A từ bộ nhớ, lấy số B, đưa vào bộ tính toán (ALU), chạy lệnh cộng, rồi cất kết quả đi. Quá trình này mất nhiều nhịp xung nhịp.

- Phần cứng (FPGA Artix-7): Bạn kết nối các cổng logic thành một “chuỗi” bộ cộng. Ngay khi bạn gạt Switch trên bo AIOT-ARTIX7, dòng điện “chảy” qua các cổng logic và kết quả xuất hiện ở đèn LED ngay lập tức. Nếu bạn cần cộng 100 cặp số cùng lúc, FPGA chỉ đơn giản là tạo ra 100 bộ cộng vật lý chạy song song.

2.5. Giao tiếp với bo mạch AIOT-ARTIX7

Chúng ta sẽ thiết kế một bộ cộng 2-bit đơn giản để thực hành:

- Đầu vào: SW1, SW2 (Số thứ nhất) và SW3, SW4 (Số thứ hai).

- Đầu ra: Các đèn LED1, LED2, LED3.

- Hoạt động: Khi bạn gạt SW1=1 và SW3=1 (phép cộng 1 + 1 nhị phân), LED1 sẽ tắt nhưng LED2 (đại diện cho số nhớ) sẽ sáng lên. Bạn đang thực sự nhìn thấy dòng điện thực hiện phép tính toán ngay trước mắt mình!

3. Tổng kết

- Kết quả phép cộng: Luôn luôn bao gồm hai thành phần: Tổng (Sum) và phần Nhớ (Carry).

- Cấu trúc: Full Adder là khối xây dựng cơ bản cho phép chúng ta cộng các số có nhiều chữ số bằng cách truyền số nhớ liên tục qua các hàng.

- Sức mạnh Artix-7: FPGA có các khối “Carry Chain” chuyên dụng giúp việc cộng các số lớn diễn ra nhanh hơn bất kỳ vi xử lý thông thường nào.

- Tư duy: Thiết kế phần cứng là tạo ra các “con đường” vật lý cho dữ liệu chảy qua để ra kết quả, không phải là viết các bước thực hiện.

Kiểm tra kiến thức

Hãy hoàn thành các câu hỏi sau để kiểm tra tư duy về cách máy tính thực hiện phép tính.

- Câu 1: Trong phép cộng nhị phân 1 bit, kết quả của 1 + 1 là gì?

A. Sum = 1, Carry = 1

B. Sum = 0, Carry = 1

C. Sum = 1, Carry = 0

D. Sum = 0, Carry = 0

Xem đáp án & Giải thích

Đáp án đúng: B

Giải thích: 1 + 1 = 10 trong hệ nhị phân. Trong đó, chữ số 0 là Tổng (Sum) và chữ số 1 là phần Nhớ (Carry).

- Câu 2: Bộ cộng nào có khả năng nhận thêm “Số nhớ” từ hàng trước đó đưa vào?

A. Half Adder (Bộ cộng bán phần)

B. Full Adder (Bộ cộng toàn phần)

C. Decoder (Bộ giải mã)

D. Multiplexer (Bộ chọn)

Xem đáp án & Giải thích

Đáp án đúng: B

Giải thích: “Full” (Toàn phần) có nghĩa là bộ cộng hỗ trợ đầy đủ cả 3 đầu vào: số thứ nhất A, số thứ hai B và số nhớ Carry-in từ hàng trước.

- Câu 3: Để tính phần “Số nhớ” (Carry) trong một bộ cộng bán phần (Half Adder), chúng ta sử dụng cổng logic nào?

A. OR

B. NOT

C. AND

D. XOR

Xem đáp án & Giải thích

Đáp án đúng: C

Giải thích: Trong phép cộng 1-bit, số nhớ chỉ bằng 1 khi cả A VÀ B đều bằng 1. Điều này tương ứng hoàn hảo với chức năng của cổng AND.

- Câu 4: Tại sao FPGA có thể thực hiện phép nhân nhanh hơn vi điều khiển?

A. Vì FPGA dùng ít điện hơn.

B. Vì phép nhân thực chất là nhiều phép cộng song song, và FPGA có thể thực hiện tất cả chúng cùng một lúc.

C. Vì FPGA có bộ nhớ RAM lớn hơn.

D. Vì FPGA không cần dùng xung nhịp (Clock).

Xem đáp án & Giải thích

Đáp án đúng: B

Giải thích: Đây là ưu điểm tuyệt đối của kiến trúc song song. Thay vì cộng từng bước một cách tuần tự, FPGA tạo ra hàng loạt bộ cộng vật lý để xử lý đồng thời.

- Câu 5: Nếu bạn muốn thiết kế bộ cộng 8-bit (cộng hai số từ 0 đến 255), bạn cần kết nối bao nhiêu bộ Full Adder lại với nhau?

A. 1 cái

B. 4 cái

C. 8 cái

D. 16 cái

Xem đáp án & Giải thích

Đáp án đúng: C

Giải thích: Mỗi bit dữ liệu cần một bộ cộng để xử lý. Để cộng hai số 8-bit, ta cần 8 bộ Full Adder nối tiếp nhau để truyền số nhớ từ bit thấp lên bit cao.

“Chúc mừng bạn đã hoàn thành Module 2! Bạn đã biết dùng cổng logic để làm mọi thứ, từ chọn luồng dữ liệu đến làm toán. Ở Module tiếp theo, chúng ta sẽ khám phá ‘phép màu’ bên trong con chip FPGA để hiểu tại sao nó làm được tất cả những điều này.”